Intel CvP 及其实现流程

一、Intel CvP 简介

CvP(Configuration via Protocol)是一种通过协议实现配置的方案, Arria® V,Cyclone® V,Stratix® V,Arria® 10,Cyclone® 10 GX,Stratix® 10,Agilex™都支持这个功能,但支持的模式有所差异。目前所采用的协议是PCI Express® (PCIe)。

CvP配置文件被拆分成两个:periphery image 及 core image

- Periphery image (*.periph.jic) 包含GPIOs,I/O registers,GCLK、QCLK、RCLK 时钟网络,PLLs,收发器,存储器PHY接口,以及硬核IP,例如PCIe硬核。这部分不能被更改和更新。Periphery image存储在FPGA配置芯片内,上电加载。

- Core image (*.core.rbf) 包含被configuration RAM (CRAM)配置的逻辑部分,包括LABs, DSP, 和embedded memory。FPGA设备上电后主机端再经由所用的协议(此处为PCIe)将core image下载并配置到FPGA内部。

二、CvP 系统结构

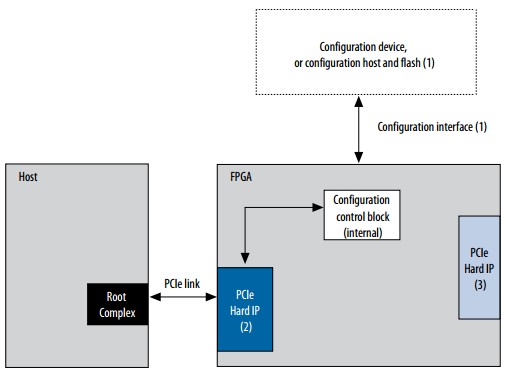

CvP系统由三部分组成:FPGA,PCIe host,FPGA的配置器件

CvP系统结构图如下图(图1)所示:

- 配置器件与FPGA通过传统配置接口互联。对于V系列和Arria10器件来说,可支持任何配置方式,例如AS,PS或FPP。但是针对Stratix10和Agilex系列器件,只可采用AS(fast mode)。

- 对于V系列、Arria10、Stratix10、Cyclone10GX,只有器件底部左侧的PCIe硬核才支持CvP功能,其他的PCIe硬核可作常规功能使用。而对于Agilex系列,左侧的PCIe硬核都支持CvP功能。在硬件设计阶段需要确认使用哪个PCIe做CvP,一旦确定,则只有这个PCIe硬核作为Endpoint可以使能CvP功能,其他PCIe硬核不能再作此用途,但可作为常规PCIe接口用。

- 其他PCIe硬核能作为常规PCIe接口使用。

三、CvP 价值

- 由于只需要存储periphery logic,FPGA的配置器件可以选择小容量器件,降低成本。

- Core image存在主机端,提高核心逻辑的安全性。

- 对于支持CvP Update Mode的器件来说,可支持动态的核心逻辑更新,而不需要系统断电重启。

- 主机侧提供了简单的软件配置模型。

四、CvP 模式

CvP的两种模式:CvP Initialization mode 和 CvP Update mode

4.1 CvP Initialization Mode初始化模式

FPGA在上电时加载配置芯片上的peripheral image,在100ms的枚举时间内成功配置其PCIe接口,使主机能正确枚举该PCIe设备。主机启动后再通过PCIe链路配置FPGA核心逻辑。

CvP Initialization Mode优势:

保证FPGA PCIe设备满足枚举时间。

FPGA的配置器件可以选择小容量器件,降低成本。

保证主机侧核心逻辑的安全性。

4.2 CvP Update Mode更新模式

当FPGA进入用户模式,对除CvP PCIe核之外的其他逻辑通过CvP进行重新配置,此时CvP PCIe既可以做常规PCIe使用,又可以实现FPGA核心逻辑的更新。为使用该模式,需要参考Partition的流程对工程进行分模块Partition和Logic Lock设计,以重复利用设备外设,保证peripheral image不变。

当有以下几种需要时,可以考虑使用该模式:

- 需要对核心逻辑进行更新。

- 根据功能发布情况对设备进行更新。

4.3 不同器件系列支持的模式

前面说到ArriaV,CycloneV,StratixV,Arria10,Cyclone10GX,Stratix10,Agilex都支持CvP,但不同系列器件支持的模式有所差异,具体如(表1),其中Agilex只支持Initialization Mode,如(表2)。

| 器件系列 | 支持的CvP模式 | ||

|---|---|---|---|

| PCIe Gen1 | PCIe Gen2 | PCIe Gen3 | |

| Stratix 10 | CvP Initialization CvP Update | CvP Initialization CvP Update | CvP Initialization CvP Update |

| Arria 10 | CvP Initialization | CvP Initialization | CvP Initialization |

| Cyclone 10 | CvP Initialization | CvP Initialization | No Support |

| Stratix V | CvP Initialization | CvP Initialization CvP Update | No Support |

| Arria V GZ | CvP Initialization CvP Update | CvP Initialization CvP Update | No Support |

| Arria V | CvP Initialization CvP Update | CvP Initialization | No Support |

| Cyclone V | CvP Initialization CvP Update | CvP Initialization | No Support |

表1 不同器件系列支持的模式

| 器件系列 | 支持的CvP模式 | |||

| PCIe Gen3 x16 | PCIe Gen4 x16 (P- tile) | PCIe Gen4 x8 | PCIe Gen3 x8 | |

| Agilex | CvP Initialization | |||

表2 Agilex系列支持的模式

五、CvP Initialization mode 实现流程和注意事项

使用Stratix V 开发板实现CvP Initialization mode 的流程及注意事项

- 板卡:Stratix-V GX Dev Kit (PCIe board),PCIe Gen1x8。

- 主机:64位Windows7操作系统。

- Quartus版本:Quartus II 64-Bit Version 14.1.0 Build 186。

5.1 实现流程

1. 构建含PCIe IP的工程,此处采用S5 PCIe的Example design。

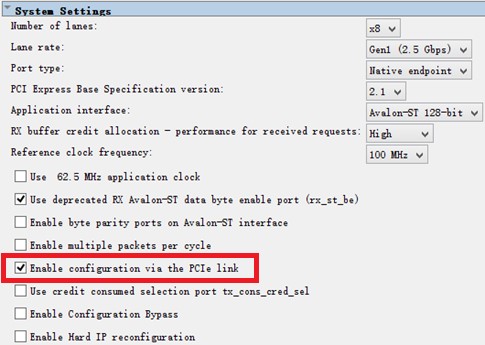

2. 打开工程内PCIe IP的GUI,勾选“Enable configuration via the PCIe link”。

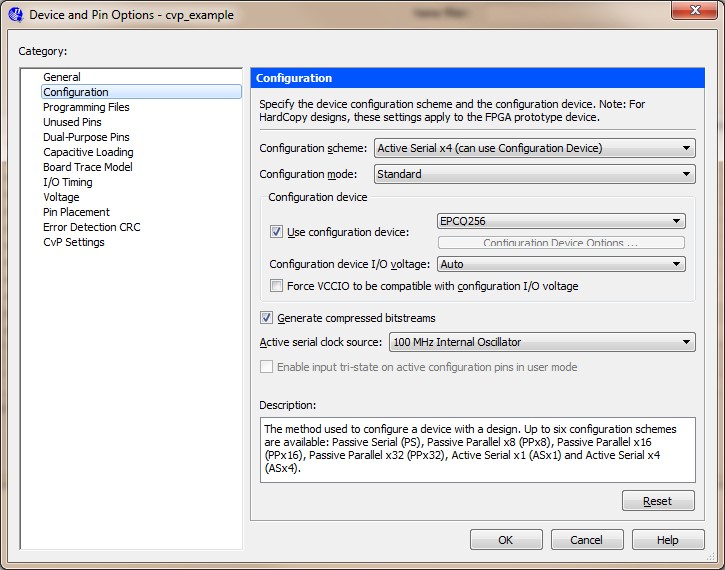

3. 在Assignments => Device => Device and Pin Options => Configuration中选择FPGA的配置模式为Active Serial x4(并设置MSEL)。

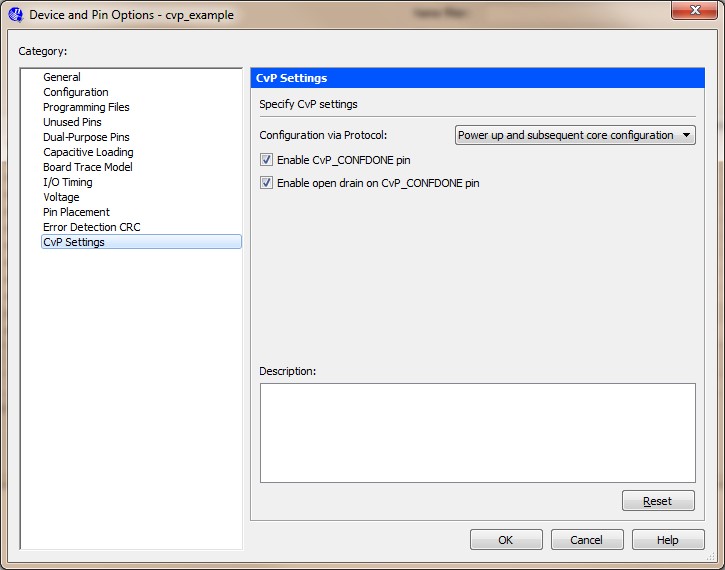

在Assignments => Device => Device and Pin Options => CvP Settings选择configuration via protocol为Core initialization。

4. 根据开发板分配管脚并编译工程,生成cvp_example.sof。

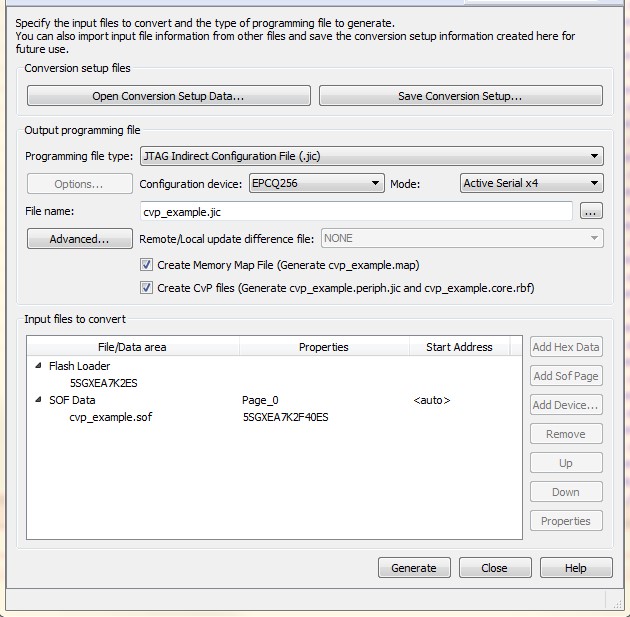

5. 将生成的cvp_example.sof进行拆分,打开File => Convert Programming Files,设置Programming file type为JTAG Indirect Configuration File (.jic)。添加cvp_example.sof,勾选Create Memory Map File和Create CvP files。点击Generate之后,cvp_example.sof就被拆分成两部分,cvp_example.periph.jic和cvp_example.core.rbf。

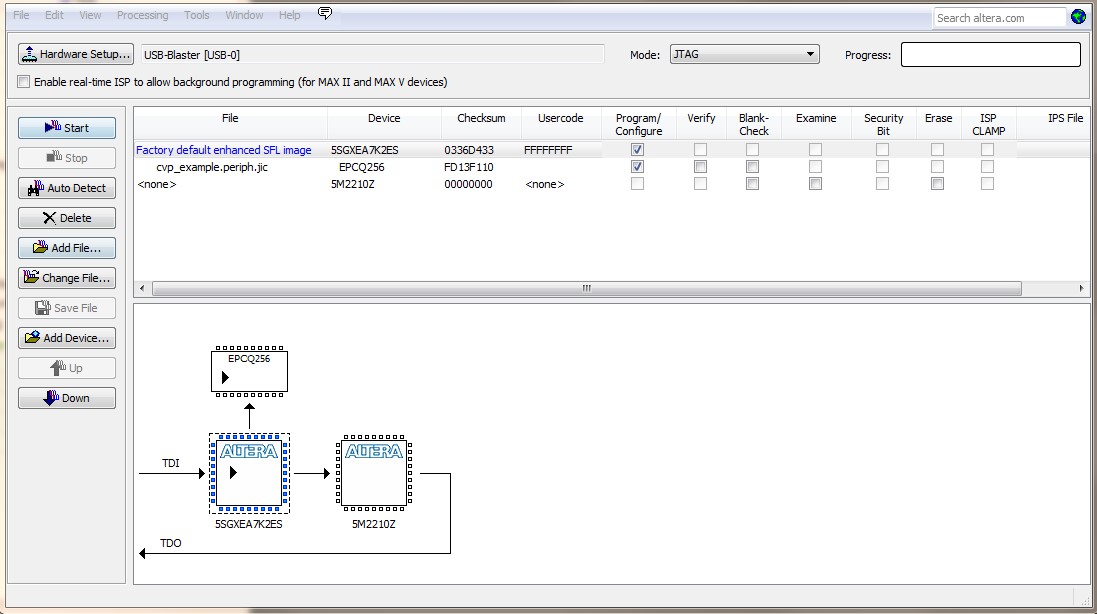

6. 关闭主机,将PCIE板卡连上JTAG,插在主机PCIe插槽里,主机再上电启动。此时PCIE板卡由PCIE插槽供电。打开Quartus II Programmer,点击Auto Detect扫描JTAG链,选择FPGA点击Change File,选择之前生成的cvp_example.periph.jic文件,并烧写进EPCQ256。

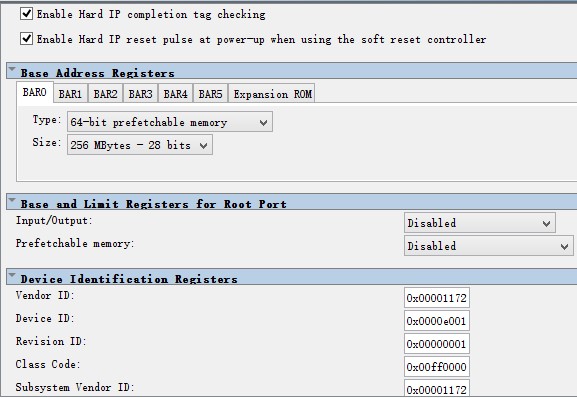

7. 重新启动主机,枚举PCIe设备。此时已经加载了cvp_example.periph.jic的PCIE板卡将作为PCIE设备被系统识别。根据PCIe IP的设置,在主机侧查看Device ID为E001,Vendor ID为1172的PCIe设备。

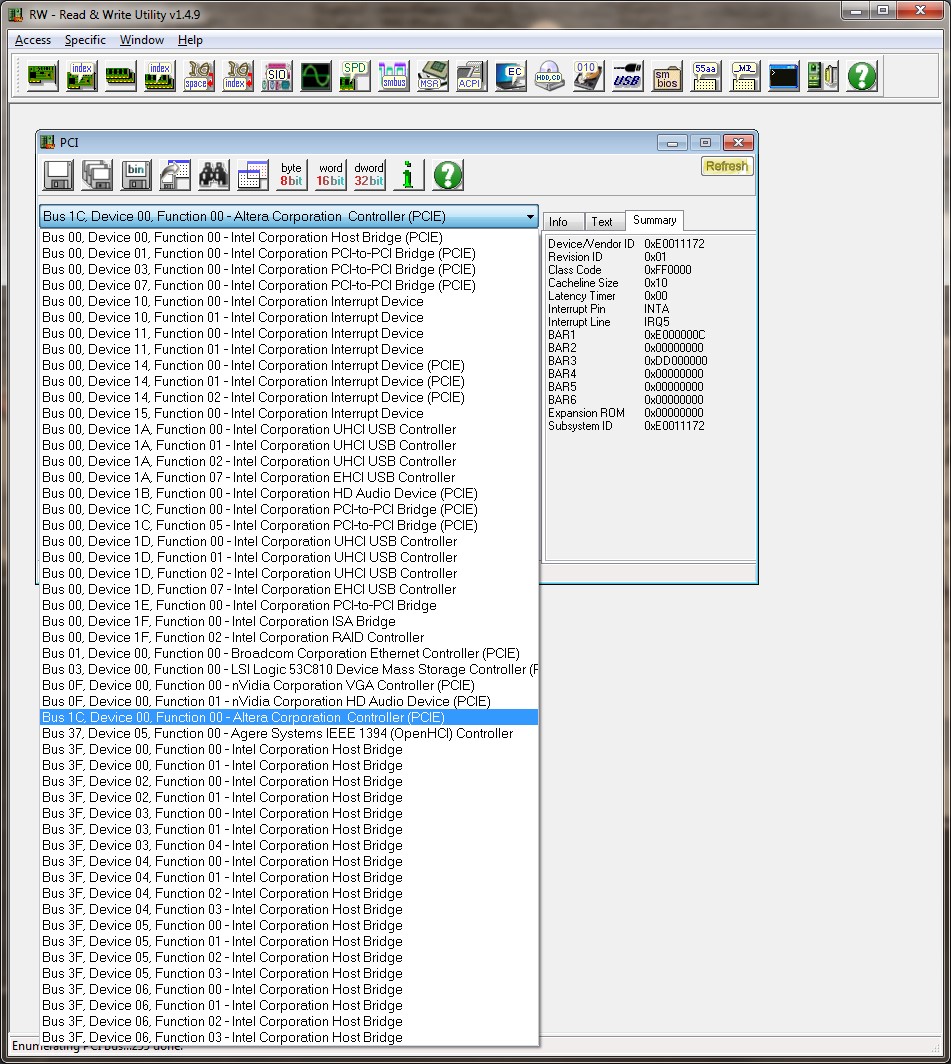

此时可以下载一个免费软件“RW – Read & Write Utility”。找到Device ID为E001,Vendor ID为1172的PCIe设备。

8. 在主机上使用quartus_cvp对识别到的PCIe板卡(Device ID为E001,Vendor ID为1172)加载核心逻辑部分cvp_example.core.rbf。打开Windows CMD,更改路径到cvp_example.core.rbf所在的位置。

输入如下命令并回车:

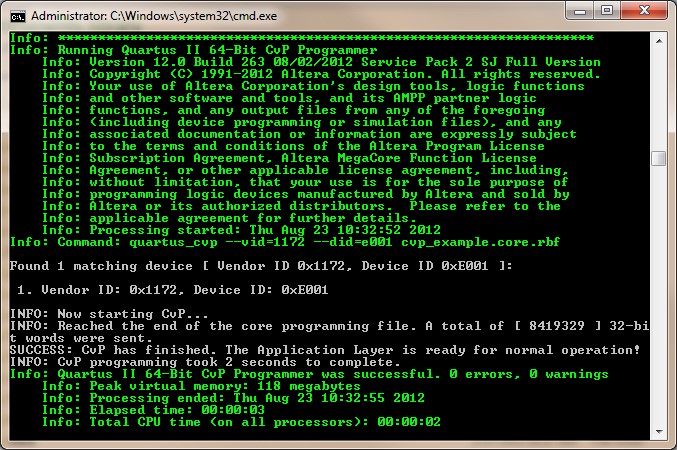

quartus_cvp --vid=1172 --did=e001 cvp_example.core.rbf 如果成功执行该命令,会出现如下界面,表示核心逻辑已被成功加载进FPGA,此时FPGA进入user mode,可以正确工作。

5.2 注意事项

运行quartus_cvp时需要安装Jungo WinDriver。

5.2.1 在Windows上安装步骤为:

1. 指向 <Quartus installation path>\quartus\drivers\wdrvr\windows[32|64] 并运行如下指令:

a. wdreg -inf windrvr6.inf install

b. wdreg -inf s5_cvp.inf install

(此处以Stratix V为例。如果设备还没有插入主机,则使用preinstall 代替install。)

2. 将wdapi1021.dll 拷贝到%windir%\system32路径下。

3. 现在就可以使用quartus_cvp将核心逻辑RBF文件下载到FPGA。

a. 指向<Quartus installation path>\quartus\bin

b. quartus_cvp --vid=<Vendor ID> --did=<Device ID> <Core RBF file path>

5.2.2 在Linux上安装步骤为:

1. 指向 <Quartus installation path>/quartus/drivers/wdrvr/linux[32|64] 并运行如下指令:

a. ./configure --disable-usb-support

b. make

c. su

d. make install

2. 更改/dev/windrvr6文件的权限,例如chmod 666 /dev/windrvr6。

3. 如果是64位 Linux系统,在运行quartus_cvp前设置QUARTUS_64BIT环境变量export QUARTUS_64BIT=1。

4. 现在就可以使用quartus_cvp将核心逻辑RBF文件下载到FPGA。

a. 指向<Quartus installation path>\quartus\bin

b. ./quartus_cvp --vid=<Vendor ID> --did=<Device ID> <Core RBF file path>

六、总结

本文介绍了Intel CvP功能的概念、优势、initialization和Update两种模式,以及CvP initialization模式的具体实现步骤。对于当前随着FPGA的逻辑规模越来越大,怎么保证基于FPGA的PCIe插卡在100ms的PCIe枚举时间内完成配置这个问题,CvP initialization模式提供了一个简单有效的解决方案。CvP的另一种模式:update模式,是对于有内核逻辑更新需求的场合的一套解决方案,本文虽没有具体介绍这个功能的实现,但Intel提供了详细的UG,欢迎参考、试验和交流,您可请点击下方「联系我们」,提交您的需求,我们骏龙科技公司愿意为您提供更深入的讲解与介绍。

更多信息:

微信平台

微信平台

FPGA 微信平台

FPGA 微信平台

領英 LinkedIn

領英 LinkedIn